CC1310 私有协议、TI-15.4、Contiki 开发

关于我们

入门开始

视频教程

CC1310平台

外设驱动

私有协议

TI-15.4(基于802.15.4g)

Contiki

工具集

其他

CC1310 私有协议、TI-15.4、Contiki 开发

关于我们

入门开始

视频教程

CC1310平台

外设驱动

私有协议

TI-15.4(基于802.15.4g)

Contiki

工具集

其他

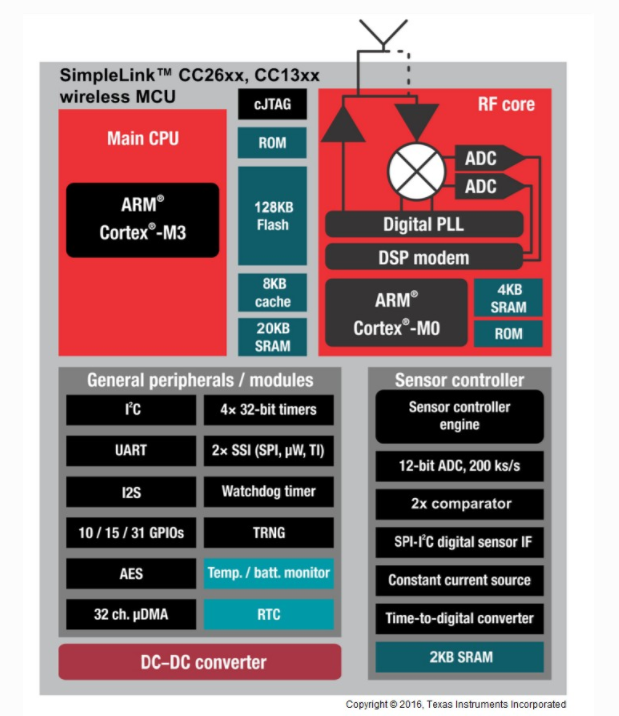

TI低功耗蓝牙软件开发套件(ble-stack SDK)是开发单模低功耗蓝牙应用的完整软件平台。该SDK基于完整的片上系统(SoC)低功耗蓝牙解决方案SimpleLink CC1310。CC1310结合了2.4GHz RF收发器,128KB系统可编程存储器,20KB SRAM以及丰富的外设。它有一个ARM® Cortex®-M3 系列的处理器用来处理应用程序和蓝牙低功耗协议栈,一个ARM Cortex®-M0 处理器来处理所有底层的无线电控制以及相关的物理层和部分链路层。 传感器控制器模块能够独立于Cortex-M3处理器进行自主数据采集和控制,从而提供了额外的灵活性,进一步扩展了CC2640R2F的低功耗能力。下图显示了模块框图。有关CC1310的更多信息,请参见CC13x0 Technical Reference Manual。

如上所示框图,我们不难看出CC1310包含三个物理内核,每个CPU既可独立使用,也可共享RAM/ROM,3个CPU各司其职又协同工作,最大程度实现了性能和功耗平衡。

系统内核(CM3)是设计用来运行低功耗蓝牙协议栈的链路层到用户应用程序的。链路层通过位于RF门铃上方称为RF驱动器的软件模块连接到无线电内核。RF驱动器在CM3上运行,并在CC1310上作为与无线电的接口,并且还管理无线电硬件和内核的电源域。有关RF驱动程序的文档,请参见TI-RTOS Drivers Reference。RF驱动器上面的就是TI低功耗蓝牙协议栈,它是在库代码中实现的。

协议栈和应用都工作在改M3和他的128Flash,一定注意区分,我们上面到过App+stack工程管理方式,整个App+Stack都是运行在该CPU上面,而不是错误理解为App工作在M3,Stack协议栈工作在M0。

CC1310内的Cortex M0(CM0)内核负责与无线电硬件相连接以及将来自Cortex M3(CM3)内核的复杂指令转换为可以通过无线电发送的数据。对于低功耗蓝牙协议,CM0实现协议栈的物理层(PHY)。通常,CM0能够自主运行,从而将CM3释放出来处理更高级别的协议和应用层。

CM3通过一个称为RF门铃的硬件接口与CM0进行通信,这在CC13x0 Technical Reference Manual的第23.2节中有说明。

对于这里的CM0,不提供用户编程,由TI出厂固化好,M3通过寄存器写入命令原语和共享RAM方式实现彼此通信,对于BLE这样的高级协议栈,几乎屏蔽了物理层操作,所以我们几乎不用关心这里的CM0。对于一些基于物理层(CC13x0)的私有协议开发,可能会设计部分。

功耗优化的16位单片机,具有的2KSRAM,负责一些外设控制、ADC采样、SPI通信等。在系统CPU休眠的时候,SC能够独立工作,这样的设计极大降低了系统CPU唤醒频率,从而减少功耗。

和Cortex-M0我们不需要关心不同,这的SensorControl我们必须熟悉其原理、开发。我们会将其放在SensorController 章节统一讲解。

对于存储系统我们必须要以下认识:

注意:以上存储空间映射图未包含完整功能寄存器和外设,完整存储映射图点击C:\ti\simplelink_cc13x0_sdk_1_40_00_10\docs\driverlib_cc13xx_cc26xx\cc13x0\register_descriptions\CPU_MMAP\CPU_MMAP.html

熟悉以上存储空间映射图,和各个存储器起始地址对于我们以后把控代码工程至关重要。

文章所有代码、工具、文档开源。加入我们QQ群 591679055获取更多支持,共同研究CC2640R2F&BLE5.0。